LaTeX 渲染有问题。将就着看吧。

# 寄存器

# 分类

用户可见寄存器

通用寄存器

数据寄存器

地址寄存器

条件码寄存器

控制和状态寄存器

程序计数器 PC

指令寄存器 IR

存储器地址寄存器 MAR

存储器缓冲寄存器 MBR(或者说是 MDR)

程序状态字 PSW

设计出发点:对操作系统的支持 / 控制信息在寄存器和存储器之间的分配

两者的区分并不严格

# 微操作

# 微操作分组的原则

事件的流动顺序必须是恰当的

必须避免冲突

满足上述条件下,所用的时间单位尽可能少

# 子周期

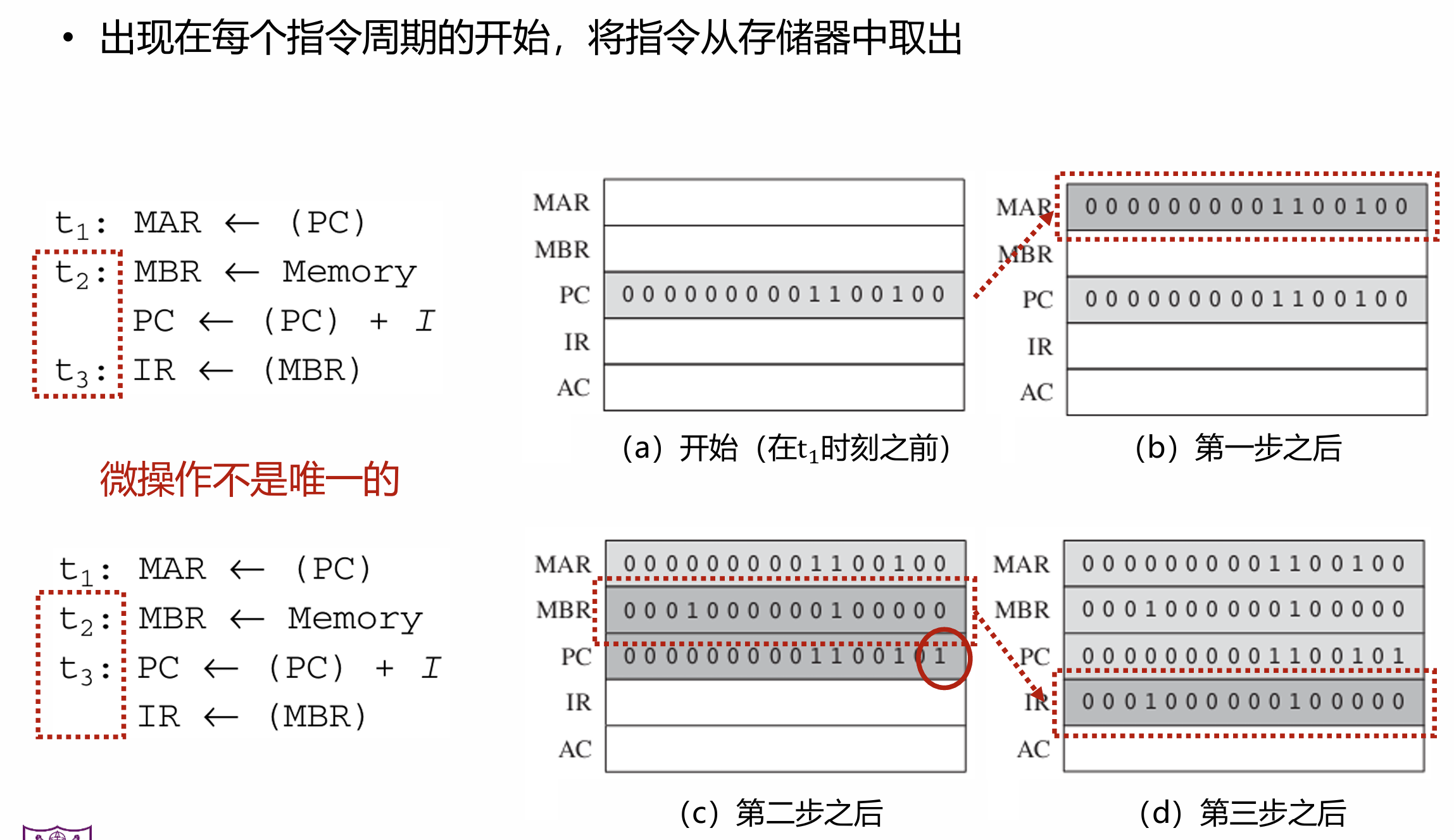

取指周期

间址周期

如果指令采用间接寻址,则在指令执行前有一个间址周期

完成间址周期后,IR 的状态与不使用间接寻址方式的状态是相同的,已经为执行周期准备就绪

![d024815799acb7ad9c48d35841d71c14.png]()

即将 IR 存储指令内的地址部分存入 MAR,读出数据后存入 MBR,MBR 将更新后的地址再存入 IR 指令内的地址部分

执行周期

中断周期

在完成执行周期时,要确定是否有允许的中断产生

如果有,则出现一个中断周期

下图是微操作示意。注意微操作的分组

# 指令周期代码 ICC

00:取指

01:间址

10:执行

11:中断

# 控制器

# 输入

指令寄存器:当前指令的寻址方式和操作码

标志:确定 CPU 的状态和前一个 ALU 操作的结果

时钟:控制器要在每个时钟脉冲完成一个或一组同时的微操作

来自控制总线的控制信号:向控制器提供控制

信号(请求)比如中断请求

# 输出

控制信号

CPU 内

控制总线

- 存储器、IO 模块

控制门的开关,从而控制数据传递

所有的控制信号最终作为二进制输入量直接输入到各个逻辑门上

# 控制器的最小特性

它只需要知道将被执行的指令和算术、逻辑运算结果的性质(如正负、溢出 等),而不需要知道正被处理的数据或得到的实际结果具体是什么

它只是以少量的送到 CPU 内的和送到系统总线上的控制信号来实现控制

# 功能需求

# CPU 的基本元素

ALU,寄存器组,内部数据通路,控制器,外部数据通路

# CPU 需要完成的微操作

在寄存器之间传送数据

将数据由寄存器传送到外部接口(如系统总线)

将数据由外部接口传送到寄存器

将寄存器作为输入和输出,完成算术和逻辑运算

# 实现

硬布线实现(hardwired implementation)

微程序实现(microprogrammed implementation)

# 硬布线实现

控制器是一个组合电路,把输入逻辑信号转换为一组输出逻辑信号,即控制信号

# 微程序实现

控制逻辑是微程序指定的,控制器是一个相对简单的逻辑电路,通过执行每条微指令来产生控制信号

微程序(固件)介于硬件与软件之间

优点与缺点:

优点

简化了控制器的设计任务

实现起来既成本较低,也能减少出错机会

便于更新

缺点

- 要比采用相同或相近半导体工艺的硬布线控制器慢一些