LaTeX 渲染有问题。将就着看吧。

能否将外设直接连接到系统总线上?不可以

为什么不能把外设直接连接到系统总线上

外设种类繁多,操作方法多种多样

外设的数据传送速度一般比存储器或处理器的慢得多

某些外设的数据传送速度比存储器或处理器要快

外设使用的数据格式和字长度通常与处理器不同

# I/O 模块

I/O 模块是计算机内部系统和外设之间的桥梁

# 功能

# 处理器通信

命令译码,状态报告,数据,地址识别

# 设备通信

通信内容包含命令、状态信息和数据

# 数据缓冲

# 控制和定时

# 检错

# 外部接口

并行接口:多根线

串行接口:一根线

# 操作技术

# 编程式 I/O

轮询?

I/O 不会中断处理器,因此处理器需要周期性地检查 I/O 模块的状态,直到发现该操作完成

CPU 全程 100% 投入

为了执行 I/O 操作,处理器发送一个指定具体 I/O 模块和外设的地址,并发送一条 I/O 命令

I/O 指令很容易映射为 I/O 命令,并且两者之间通常是简单的一一对应关系

编址方式

存储器映射式 I/O:合并到指令系统里

分离式 I/O:有独立的线

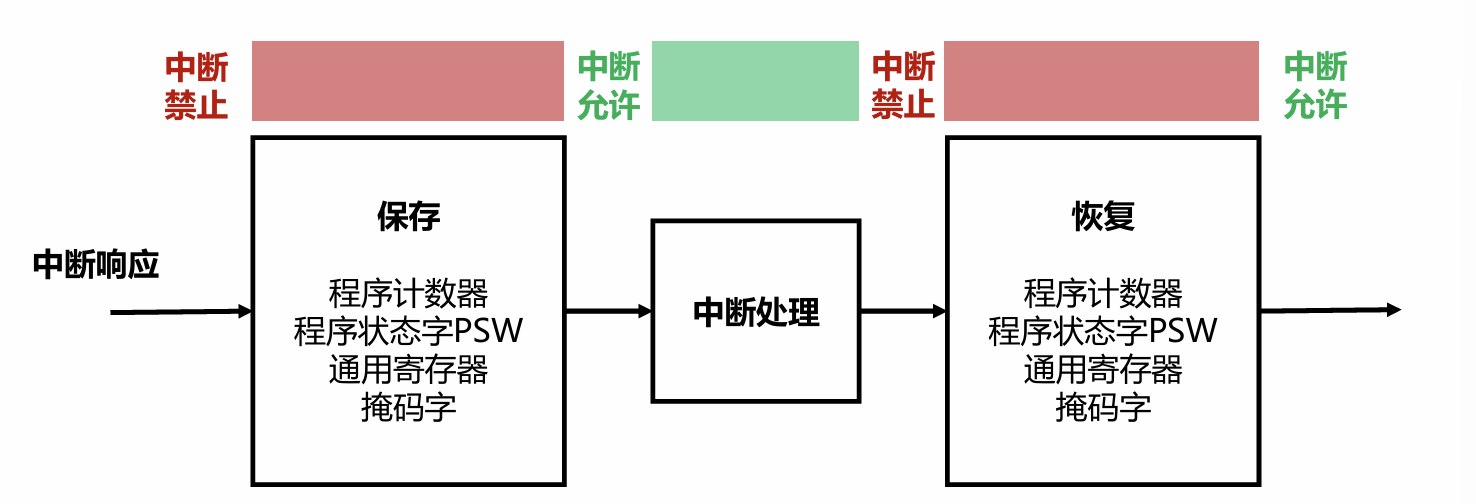

# 中断驱动式 I/O

中断处理器来进行 I/O 操作

# 响应优先级和处理优先级

响应优先级:

响应优先级决定了中断控制器在接收到多个中断信号时,应该优先响应哪一个中断请求。

响应优先级仅涉及哪一个中断首先被响应,不直接决定中断的具体处理时间。

处理优先级:

处理优先级决定了 CPU 在响应中断后,如何分配资源来处理这些中断。

处理中断时,可能出现嵌套中断的情况,此时需要根据处理优先级决定是否允许其他中断打断当前中断。

举例:如果当前正在处理一个低优先级的中断,但又有一个高优先级的中断到来,则高优先级中断可以中断低优先级中断的处理(称为嵌套中断)。

** 例子:** 假设中断系统中有 4 个中断源,其响应优先级为 L1>L2>L3>L4,处理优先级为 L1>L4>L3>L2。如果在主程序执行时同时发生 L1、L3 和 L4 中断,并且在处理 L3 中断的过程中发生 L2 中断,写出掩码字和所有中断服务程序的过程。

** 掩码字:** 为 1 代表可打断,为 0 代表不可打断

# 直接存储器存取(DMA)

直接存储器存取:无需经过处理器即可直接访问内存的模块

DMA 模块将全部数据块,每次一个字,直接将数据传输到存储器或从存储器读出,而无需经过处理器

传输完成时,DMA 模块向处理器发送一个中断信号

内存访问时,DMA 优先于 CPU

# 内存访问

# CPU 停止法

直接打断 CPU?

优点:控制简单

缺点:影响 CPU,没有充分利用内存

适用:高速 I/O 设备的块传输

# 周期窃取

在 CPU 访问的间隔期使用 DMA?

适用:I/O 周期大于存储周期

# 交替分时访问

优点:CPU 未停止或等待,DMA 不请求总线

缺点:CPU 周期大于存储周期

# 配置机制

# 单总线分离 DMA

所有模块共享相同的系统总线

DMA 直接连在总线上

# 单总线集合的 DMA-I/O

DMA 逻辑实际上可能是 I/O 模块的一部分,也可能是控制一个或多个 I/O 模 块的单独模块

# I/O 总线

使用 I/O 总线将 I/O 模块连接到 DMA 模块

多个 I/O 模块共享 DMA,且易于扩展